## 2:1 Mux/DeMux High Bandwidth HDMI<sup>™</sup> 2.1 Compliant Signal Switch

## **Descriptions**

RLCS416 series of switch circuits are targeted for high-resolution video network that are based on DVI/HDMI<sup>TM</sup> standard, and TMDS signal process. The RLCS416 is an 8- to 4-Channel Mux/DeMux Switch. The device multiplexes differential signals to one of two corresponding outputs. The switch is bidirectional and offers little or no attenuation of the high-speed signals at the outputs. It is designed for low bit-to-bit skew and high channel-to-channel noise isolation.

The high bandwidth provides the resolution required by the next generation HDTV and PC graphics. Three differential channels are used for data (video signals for DVI or audio/video signals for HDMI), and one differential channel is used for Clock for decoding the TMDS signals at the outputs.

Because of its passive bidirectional feature, this switch can be used either at the video drivers side or at the receiver side. For PC graphics applications, the device sits at the drivers side to switch between multiple display units such as LCD monitor, projector, TV, etc. For consumer video applications, the device sits at the receiver end to switch between the source components such as DVD, D-VHS, STB, etc.

The wide voltage range allow DC-coupled multi-standard operation. Eliminating AC coupling capacitors saves board space and improves signal integrity for dense PCB design. The high speed channels can also pass 0V-3.3V CMOS signals up to 1MHz. In addition to four high-speed lanes, RLCS416 also switches the CEC, DDC and HPD signals.

#### **Features**

- 4-Differential Channel 2:1 Mux/DeMux

- ➤ HDMIT 2.1 compatible

- ➤ High Bandwidth: 5.7GHz @-3dB BW

- > Supports both AC coupled and DC coupled signals

- ➤ Isolation: -40dB @ 2.0 Gbps

- Crosstalk: -31dB @ 2.0 Gbps

- ➤ ESD Tolerance: 2kV HBM

- > Low bit-to-bit skew, Bidirectional

- Supports DDC with HPD channel mux/demux @ HDMI

- Supports 720 Mbps high-speed DP AUX @ DP

## **Applications**

- Routing of HDMI 2.1 video signals with low signal attenuation between source and sink for 4K2K ultra high definition video display and broadcast video equipment.

- Routing of DisplayPort video signals with low signal attenuation between source and sink for PC and monitor.

### **Order information**

| Pack          | age           | Part Number    | Quantity per Reel |

|---------------|---------------|----------------|-------------------|

| QFN 9×3.5-42L | Tape and Reel | RLCS416QN42/R6 | 3000PCS           |

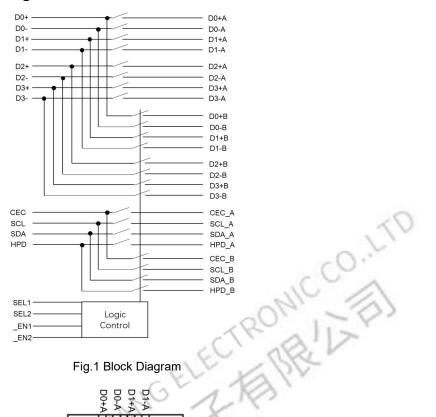

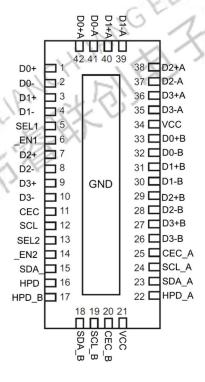

## **Block Diagram and Pin Configuration**

Fig.1 Block Diagram

Fig.2 Top-Through View

## **Truth Table**

| _EN1 | SEL1 | D0-D3 |

|------|------|-------|

| High | Х    | Hi-Z  |

| Low  | Low  | Α     |

| Low  | High | В     |

| _EN2 | SEL2 | CEC  | SCL  | SDA  | HPD  |

|------|------|------|------|------|------|

| High | X    | Hi-Z | Hi-Z | Hi-Z | Hi-Z |

| Low  | Low  | Α    | Α    | Α    | Α    |

| Low  | High | В    | В    | В    | В    |

**Pin Description**

| Pin# | Pin Name | Signal Type | Description                                 |  |  |  |

|------|----------|-------------|---------------------------------------------|--|--|--|

| 1    | D0+      | I/O         | Positive differential signal 0 for COM port |  |  |  |

| 2    | D0-      | I/O         | Negative differential signal 0 for COM port |  |  |  |

| 3    | D1+      | I/O         | Positive differential signal 1 for COM port |  |  |  |

| 4    | D1-      | I/O         | Negative differential signal 1 for COM port |  |  |  |

| 5    | SEL1     | I           | Switch logic control                        |  |  |  |

| 6    | _EN1     | I           | Switch logic control                        |  |  |  |

| 7    | D2+      | I/O         | Positive differential signal 2 for COM port |  |  |  |

| 8    | D2-      | I/O         | Negative differential signal 2 for COM port |  |  |  |

| 9    | D3+      | I/O         | Positive differential signal 3 for COM port |  |  |  |

| 10   | D3-      | I/O         | Negative differential signal 3 for COM port |  |  |  |

| 11   | CEC      | I/O         | Consumer electronic control for COM port    |  |  |  |

| 12   | SCL      | I/O         | DDC clock for COM port                      |  |  |  |

| 13   | SEL2     | I           | Switch logic control                        |  |  |  |

| 14   | _EN2     | I           | Switch logic control                        |  |  |  |

| 15   | SDA      | I/O         | DDC data for COM port                       |  |  |  |

| 16   | HPD      | I/O         | Hot plug detect for COM port                |  |  |  |

| 17   | HPD_B    | I/O         | Hot plug detect for B port                  |  |  |  |

| 18   | SDA_B    | I/O         | DDC data for port B                         |  |  |  |

| 19   | SCL_B    | I/O         | DDC clock for port B                        |  |  |  |

| 20   | CEC_B    | I/O         | Consumer Electronics Control for port B     |  |  |  |

| 21   | VCC      | Power       | Supply Voltage                              |  |  |  |

| 22   | HPD_A    | I/O         | Hot plug detect for port A                  |  |  |  |

| 23   | SDA_A    | 1/0         | DDC data for port A                         |  |  |  |

| 24   | SCL_A    | I/O         | DDC clock for port A                        |  |  |  |

| 25   | CEC_A    | I/O         | Consumer Electronics Control for port A     |  |  |  |

| 26   | D3-B     | I/O         | Negative differential signal 3 for port B   |  |  |  |

| 27   | D3+B     | I/O         | Positive differential signal 3 for port B   |  |  |  |

| 28   | D2-B     | I/O         | Negative differential signal 2 for port B   |  |  |  |

| 29   | D2+B     | I/O         | Positive differential signal 2 for port B   |  |  |  |

| 30   | D1-B     | I/O         | Negative differential signal 1 for port B   |  |  |  |

| 31   | D1+B     | I/O         | Positive differential signal 1 for port B   |  |  |  |

| 32   | D0-B     | I/O         | Negative differential signal 0 for port B   |  |  |  |

| 33   | D0+B     | I/O         | Positive differential signal 0 for port B   |  |  |  |

| 34   | VCC      | Power       | Supply Voltage                              |  |  |  |

| 35   | D3-A     | I/O         | Negative differential signal 3 for port A   |  |  |  |

| 36   | D3+A     | I/O         | Positive differential signal 3 for port A   |  |  |  |

| 37   | D2-A     | I/O         | Negative differential signal 2 for port A   |  |  |  |

| 38   | D2+A     | I/O         | Positive differential signal 2 for port A   |  |  |  |

| 39   | D1-A     | I/O         | Negative differential signal 1 for port A   |  |  |  |

| 40   | D1+A     | I/O         | Positive differential signal 1 for port A   |  |  |  |

| 41   | D0-A     | I/O         | Negative differential signal 0 for port A   |  |  |  |

| 42 D0+A I/O Positive differential signal 0 for port A | 42 | D0+A | I/O | Positive differential signal 0 for port A |

|-------------------------------------------------------|----|------|-----|-------------------------------------------|

|-------------------------------------------------------|----|------|-----|-------------------------------------------|

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                | -65℃ to +150℃  |

|------------------------------------|----------------|

| Junction Temperature               | 125°C          |

| Supply Voltage to Ground Potential | -0.5V to +5.5V |

| High Speed Data Channel D0~D3      | -0.5V to 3.8V  |

| CEC, SCL, SDA, HPD                 | -0.5V to 5.5V  |

| DC Input Voltage                   | -0.5V to VCC   |

| DC Output Current                  | 120mA          |

| Power Dissipation                  | 0.5W           |

## Notes:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Electrical Characteristics**

|                                                      | Parameter                                                    |                                             | Test conditions <sup>(1)</sup>                               | Min         | Typ. <sup>(2)</sup> | Max   | Unit |  |

|------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------|-------------|---------------------|-------|------|--|

| PORT A                                               | \                                                            |                                             |                                                              |             |                     |       |      |  |

|                                                      |                                                              | D0 to D3                                    | V <sub>CC</sub> =3V,                                         |             | 6.5                 | 9.5   | Ω    |  |

| R <sub>on</sub>                                      | ON-state resistance                                          | SCL,SDA,                                    | 1.5V≤V <sub>VO</sub> ≤V <sub>CC</sub> ,                      |             | _                   |       | _    |  |

|                                                      |                                                              | HPD,CEC                                     | I <sub>I/O</sub> =-40mA                                      |             | 6                   | 9.5   | Ω    |  |

| _                                                    | ON-state resistance                                          |                                             | V <sub>CC</sub> =3V, V <sub>I/O</sub> =1.5V                  |             |                     |       |      |  |

| R <sub>ON(flat)</sub> flatness                       |                                                              | All I/O                                     | and V <sub>CC</sub> ,I <sub>I/O</sub> =-40mA                 |             | 1.5                 |       | Ω    |  |

|                                                      | On-state resistance                                          |                                             |                                                              |             |                     |       |      |  |

| ΔR <sub>ON</sub>                                     | match between high-                                          | D0 to D3                                    | V <sub>CC</sub> =3V,1.5V≤V <sub>I/O</sub> ≤V <sub>CC</sub> , |             | 0.4                 | 1     | Ω    |  |

|                                                      | speed channels                                               |                                             | I <sub>I/O</sub> =-40mA                                      |             |                     |       |      |  |

|                                                      | Leakage under power                                          |                                             | V <sub>CC</sub> =0V, V <sub>I/O</sub> =0V to                 |             |                     |       | 40   |  |

| loff                                                 |                                                              | All outputs                                 | 3.6V , V <sub>IN</sub> =V to 5.5V                            |             | ±10                 |       | uA   |  |

| PORTB                                                |                                                              | •                                           |                                                              |             |                     |       | 0.   |  |

|                                                      |                                                              | D0 to D3                                    | V <sub>CC</sub> =3V,                                         |             | 8.2                 | 10.5  | 0    |  |

| R <sub>ON</sub> ON-stat                              | ON-state resistance                                          | SCL,SDA,                                    | 1.5V≤V <sub>VO</sub> ≤V <sub>CC</sub> ,                      |             |                     | 0.5   | (0)  |  |

|                                                      |                                                              | HPD,CEC                                     | I <sub>I/O</sub> =-40mA                                      | - 5         | 6                   | 9.5   | Ω    |  |

| ON-state resistance                                  | 11110                                                        | V <sub>CC</sub> =3V, V <sub>I/O</sub> =1.5V | 0                                                            | <i>∞</i> `_ | 180                 |       |      |  |

| R <sub>ON(flat)</sub> flatness                       |                                                              | All I/O                                     | and V <sub>CC</sub> ,I <sub>I/O</sub> =-40mA                 | 1           | 1.5                 | 61    | Ω    |  |

| On-state resistance                                  |                                                              | D0 to D3                                    | \\ 0\\4.5\\4\\ a\\                                           | 1           | NO.                 | 0.4 1 |      |  |

| ΔR <sub>ON</sub> match between high-                 | V <sub>CC</sub> =3V,1.5V≤V <sub>I/O</sub> ≤V <sub>CC</sub> , |                                             | 5                                                            | 0.4         | Ω                   |       |      |  |

|                                                      | speed channels                                               |                                             | I <sub>I/O</sub> =-40mA                                      | 3           | >                   |       |      |  |

|                                                      |                                                              |                                             | V <sub>CC</sub> =0V, V <sub>I/O</sub> =0V to                 |             |                     |       |      |  |

| I <sub>OFF</sub> Leakage under power off All outputs |                                                              | All outputs                                 | 3.6V , V <sub>IN</sub> =V to 5.5V                            |             |                     | ±10   | uA   |  |

| DIGITAL I                                            | NPUTS(SEL1,SEL2,EN1,EN                                       | N2)                                         | THE                                                          |             |                     |       |      |  |

| \/II.I                                               | High-level control input                                     | - 9                                         | 2                                                            | 4.4         |                     |       |      |  |

| VIH                                                  | voltage                                                      | X                                           |                                                              | 1.4         |                     |       | V    |  |

| \/II                                                 | LOW-level control input                                      | 0514                                        |                                                              |             |                     | 0.5   |      |  |

| VIL                                                  | voltage                                                      | SEL1,                                       |                                                              |             |                     | 0.5   | V    |  |

| VILL                                                 | Digital input high                                           | SEL2,                                       | V =2.6V V =V00                                               |             | 140                 |       |      |  |

| VIH                                                  | leakage current                                              | EN1, EN2                                    | V <sub>CC</sub> =3.6V, V <sub>IN</sub> =VCC                  |             |                     | ±10   | uA   |  |

| VIII                                                 | Digital input low leakage                                    |                                             |                                                              |             |                     | 140   |      |  |

| VIL                                                  | current                                                      |                                             | V <sub>CC</sub> =3.6V, V <sub>IN</sub> =GND                  |             |                     | ±10   | uA   |  |

| SUPPLY                                               |                                                              |                                             |                                                              |             |                     |       |      |  |

|                                                      |                                                              |                                             |                                                              |             |                     |       |      |  |

| $I_{CC}$                                             | VCC supply current                                           |                                             | =0,Normal operation                                          |             | 100                 |       | uA   |  |

|                                                      |                                                              |                                             | mode, _ENx=L                                                 |             |                     |       |      |  |

|                                                      | VCC supply current in power-down                             |                                             | V <sub>CC</sub> =3.6V, I <sub>I/O</sub> =0,                  |             |                     |       |      |  |

| I <sub>CC</sub> , PD                                 | voo sappiy saironi in por                                    | ioi doiiii                                  | 100 0.01, 1/0 0,                                             |             | 2                   |       | uA   |  |

### Notes:

- 1.  $V_{I}$ , Vo. I<sub>I</sub>, and I<sub>O</sub> refer to I/O pins,  $V_{IN}$  refers to the control inputs.

- 2. All typical values are at Vcc = 3.3 V (unless otherwise noted), TA = 25°C.

- 3. R<sub>(ON/FLAT)</sub> is the difference of R<sub>ON</sub> in a given channel at specified voltages.

- 4.  $\Delta R_{ON}$  is the difference of  $R_{ON}$  from center port to any other ports.

Switching Characteristics (TA= -40°C to +105°C, VCC=3.3V±10%)

| all chan Bit-to-bi of Dx± c  t <sub>ch-ch</sub> Channe | pagation delay (input pin to output pin) hannels p-bit skew within the same differential p x± channels nnel-to-channel skew of Dx+ channels | pair | 80 | 7   | ps<br>ps |

|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|----|-----|----------|

| t <sub>ch-ch</sub> of Dx± c                            | x± channels                                                                                                                                 |      | 5  |     | ps       |

|                                                        | nnel-to-channel skew of Dx+ channels                                                                                                        | ;    |    |     |          |

| Tew a h Time it t                                      |                                                                                                                                             |      |    | 35  | ps       |

| 15W a-D   TIME ILL                                     | e it takes to switch from port A to port E                                                                                                  | 3    |    | 0.1 | us       |

| Tsw b-a Time it t                                      | e it takes to switch from port B to port <i>i</i>                                                                                           | 4    |    | 0.1 | us       |

| Tstartup VCC va                                        | valid to channel enable                                                                                                                     |      |    | 10  | us       |

| Twakeup Enabling                                       | bling output by changing OE from low                                                                                                        | ı to | 0  | 10  | us       |

| LE                                                     | EN RULLANCHUANG                                                                                                                             | 23   | 76 | ,   |          |

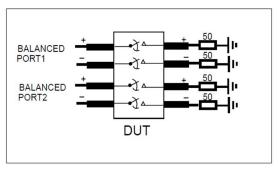

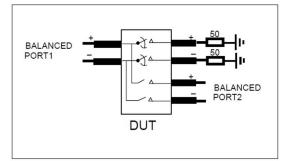

# **Dynamic Electrical Characteristics Over Operating Range (**TA= -40° to +105°C, VCC=3.3V±10%**)**

| Parameter                                          | Description                         | Test con                              | nditions         | Min. | Тур.      | Max       | Unit |

|----------------------------------------------------|-------------------------------------|---------------------------------------|------------------|------|-----------|-----------|------|

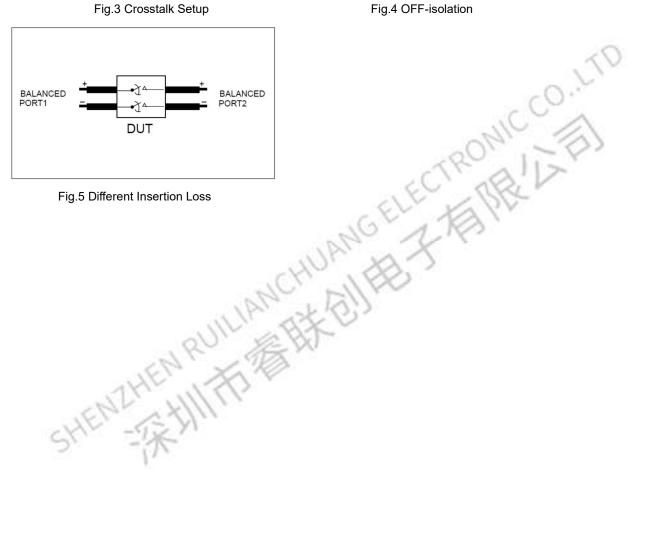

|                                                    |                                     |                                       | f = 3.0GHz       |      | -25       | -22       |      |

| X <sub>TALK</sub> Crosstalk on High Speed Channels | Crosstalk on High                   | See Fig.3 for<br>Measurement<br>setup | f = 2.7GHz       |      | -28       | -25       |      |

|                                                    | Speed Channels                      |                                       | f = 1.7GHz       |      | -31       | -28       |      |

|                                                    |                                     |                                       | f = 1.35GHz      |      | -32       | -28       | 4D   |

|                                                    |                                     |                                       | f = 3.0GHz       |      | -22       | -20       | dB   |

| OFF Isolation on OIRR High Speed Channels          |                                     | See Fig.4 for<br>Measurement<br>setup | f = 2.7GHz       |      | -22       | -20       | CO   |

|                                                    |                                     |                                       | f = 1.7GHz       | -    | -29       | -26       | 112  |

|                                                    |                                     |                                       | f = 1.35GHz      | EC   | -30       | -27       | -    |

| ,                                                  | Different Insertion                 | @3.0GHz(                              | see Fig.5)       | -2.0 | -1.7      |           | -ID  |

| ILOSS                                              | Loss on High Speed<br>Channels      | @5.4GHz(see Fig.5)                    |                  | -2.0 | -1.7      |           | dB   |

| RLoss                                              | Different Return Loss on High Speed | @3.0GHz(6.0Gbps)                      |                  |      | -<br>16.0 | -14       | dB   |

| RLOSS                                              | Channels                            | @2.7GHz(                              | @2.7GHz(5.4Gbps) |      | -<br>14.0 | -<br>12.5 | UD   |

| BW                                                 | Bandwidth -3dB                      | see F                                 |                  |      | 5.7       |           | GHz  |

#### Note:

- 1. For Max. or Min. conditions, use appropriate value specified under Electrical Characteris-tics for the applicable device type.

- 2. Typical values are at VCC=3.3V,TA=25℃ ambient and maximum loading.

Fig.3 Crosstalk Setup

Fig.4 OFF-isolation

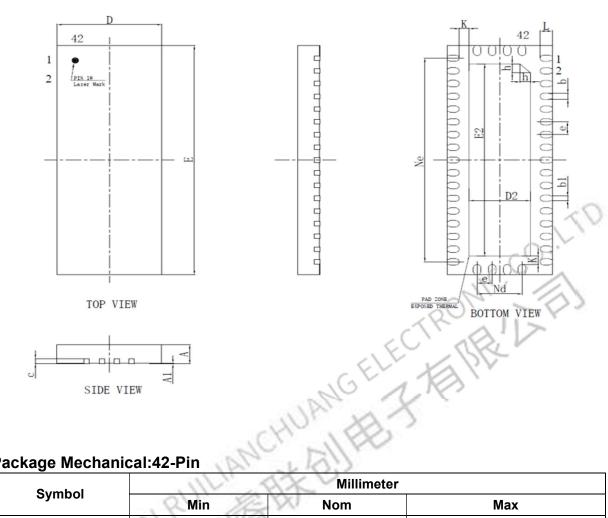

# **Package Outline Dimensions**

Package Mechanical:42-Pin

| Cumbal | Millimeter     |          |      |  |  |  |

|--------|----------------|----------|------|--|--|--|

| Symbol | Min            | Nom      | Max  |  |  |  |

| Α      | 0.70           | 0.75     | 0.80 |  |  |  |

| A1     | 0              | 0.02     | 0.05 |  |  |  |

| b      | 0.20           | 0.25     | 0.30 |  |  |  |

| b1 -   | 0.18REF        |          |      |  |  |  |

| С      | /              | 0.203REF |      |  |  |  |

| D      | 3.40           | 3.50     | 3.60 |  |  |  |

| D2     | 1.95 2.05 2.15 |          |      |  |  |  |

| е      | 0.50BSC        |          |      |  |  |  |

| Nd     | 1.50BSC        |          |      |  |  |  |

| Е      | 8.90           | 9.00     | 9.10 |  |  |  |

| E2     | 7.45           | 7.55     | 7.65 |  |  |  |

| Ne     | 8.00BSC        |          |      |  |  |  |

| L      | 0.35           | 0.40     | 0.45 |  |  |  |

| h      | 0.30           | 0.35     | 0.40 |  |  |  |

| K      |                | 0.325REF |      |  |  |  |

## **Important Note**

As the RLC product continues to improve gradually, we may experience significant changes. RLC reserves the right to correct, modify, enhance, and amend the products and services they provide, as well as the right to discontinue any product or service. Before placing an order, customers should obtain the latest information to verify that it is current and complete. All products sold must comply with RLC's terms and conditions in order to ensure proper processing of orders. RLC guarantees that the products they sell conform to the terms and conditions applicable to semiconductor sales. Only under this guarantee does RLC consider it necessary to employ testing and quality control measures for their products. Unless mandated by applicable laws requiring strict compliance, there is no obligation for testing all product parameters. RLC does not assume responsibility for customer product design or application. The materials provided contain circuit examples and usage methods solely for reference purposes; they do not guarantee suitability for volume production designs. Additionally, these materials may contain errors that could result in damages incurred by customers; therefore, RLC disclaims any liability in such cases. Customers are advised to use products within the limits specified in these materials while paying particular attention to absolute maximum ratings, operating voltages, and voltage characteristics. Any use of products outside of these specifications absolves RLC from responsibility; customers must accept full responsibility themselves. To minimize risks associated with customer-designed applications, adequate design safety measures should be implemented. When using RLC products, please ensure compliance with relevant laws and regulations pertaining to your country or region regarding application standards as well as testing requirements related to safety performance. For exports of RLC products overseas, it is essential that you adhere strictly to foreign exchange regulations and transaction laws throughout all necessary procedures involved in exportation processes. In case of disposal of any abandoned RLC product(s), please follow appropriate rules and regulations for proper disposal.

RLC products are not designed to be radiation - resistant. Based on the intended usage, customers can incorporate radiation protection measures during the product design process. Under normal circumstances, RLC products do not harm human health. However, since they contain chemicals and heavy metals, do not put them in your mouth. Additionally, the fracture surfaces of wafers and chips can be sharp. When touching them with bare hands, please be careful to avoid injury. Semiconductor products have a certain probability of failure or malfunction. To prevent disruptions and social damages resulting from personal accidents, fire accidents, etc., as well as to avoid malfunctions, customers are required to be responsible for comprehensive design, implementing fire - spread prevention measures, and safety design against misoperation. Please conduct a full assessment of the entire system, and customers can determine its applicability on their own.

This material also includes content related to the company's copyright and know - how. The records in this material are not intended to promise or guarantee the implementation and use of the company's and third - party intellectual property and other rights. Without the permission of our company, it is strictly prohibited to reprint, copy any part of this work, or disclose the material information to third parties.

RLC shall not be held responsible for any damage or harm that occurs which is not related to the product itself, as well as for any infringement of third - party rights such as intellectual property rights. For more details about this material, please contact our sales office.